# Agilent E2925B Opt. 300 PCI Exerciser

User's Guide

Agilent Technologies

#### **Important Notice**

This document contains propriety information that is protected by copyright. All rights are reserved. Neither the documentation nor software may be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form, in whole or in part, without the prior written consent of Agilent Technologies.

© Copyright 1999, 2000 by: Agilent Technologies Herrenberger Straße 130 D-71034 Böblingen Germany

The information in this manual is subject to change without notice. Agilent Technologies makes no warranty of any kind with regard to this manual, including but not limited to the implied warranties of merchantability and fitness for a particular purpose.

Agilent Technologies shall not be liable for errors contained herein or direct, indirect, special, incidental, or consequential damages in connection with the furnishing, performance, or use of this manual.

Brand or product names are trademarks or registered trademarks of their respective companies or organizations.

Authors: Stephan Greisinger and Stefan Kunzi, t3 medien GmbH

## Contents

| PCI Exerciser Ove | erview                                                | 7  |

|-------------------|-------------------------------------------------------|----|

|                   | Gaining an Active Part in Optimization and Validation | 8  |

|                   | PCI Exerciser User Interface                          | 10 |

|                   | PCI Exerciser Configurations                          | 12 |

|                   | Setting Up a PCI Exerciser Test                       | 14 |

|                   | What is a Transaction?                                | 14 |

| Running A Sample  | e PCI Exerciser Session                               | 17 |

|                   | Example Scenarios                                     | 17 |

|                   | Preparing for the Guided Tour                         | 18 |

|                   | Guided Tour: Generating Master Transactions           | 20 |

|                   | Loading the Setup Files                               | 20 |

|                   | Setting up a Master Transaction                       | 20 |

|                   | Specifying a Conditional Start                        | 21 |

|                   | Viewing the Results                                   | 22 |

|                   | Guided Tour: Specifying Custom Target Behavior        | 24 |

|                   | Loading the Setup Files                               | 24 |

|                   | Setting up the Target Decoders                        | 24 |

|                   | Specifying the Target Protocol Behavior               | 26 |

|                   | Viewing the Results                                   | 26 |

|                   | Guided Tour: Accessing VGA Frame Buffer Memory        | 27 |

|                   | Starting the Command Line Interface                   | 28 |

|                   | Entering the Required CLI Commands                    | 28 |

| The PCI Exerciser | as a Master Device                                    | 31 |

|                   | Programming Master Transactions                       | 32 |

|                   | Master Transactions Overview                          | 33 |

|                   | Transaction Properties                                | 36 |

|                   | Implementing Master Transaction Scripts               | 39 |

|                   | Controlling Master Attributes                         | 40 |

|                   | Specifying Master Attributes                          | 40 |

|                   | Master Address Phase Attributes                       | 42 |

|                   |                                                       |    |

|                  | Master Data Phase Attributes                 | 44 |  |

|------------------|----------------------------------------------|----|--|

|                  | Master Control Attributes                    | 45 |  |

|                  | Implementing Master Attribute Scripts        | 46 |  |

|                  | Running the Master                           | 47 |  |

|                  | Preparing Test Execution                     | 47 |  |

|                  | Starting the Master                          | 50 |  |

|                  | Stopping the Master                          | 51 |  |

| The PCI Exercise | er as a Target Device                        | 53 |  |

|                  | Configuration Space and Target Decoders      | 54 |  |

|                  | Configuration Space Header                   | 55 |  |

|                  | Target Decoder Properties                    | 57 |  |

|                  | Data Resources                               | 61 |  |

|                  | Target Decoder Setup                         | 63 |  |

|                  | Programming the Decoders                     | 64 |  |

|                  | Modifying the Configuration Space Header     | 66 |  |

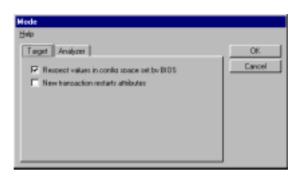

|                  | Overwriting BIOS Settings                    | 69 |  |

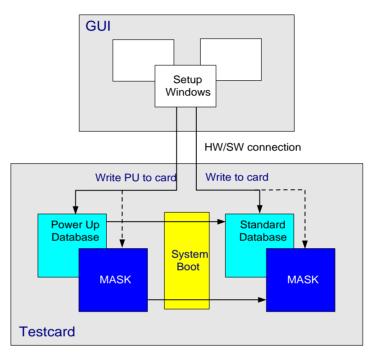

|                  | Standard and Power Up Databases              | 70 |  |

|                  | Controlling Target Attributes                | 72 |  |

|                  | Available Target Attributes                  | 72 |  |

|                  | Implementing Target Attribute Scripts        | 76 |  |

|                  | Setting the Reset Mode for Target Attributes | 78 |  |

|                  | Initializing the Target                      | 79 |  |

| Using the Data N | Using the Data Memory                        |    |  |

|                  | Organization of the Data Memory              | 82 |  |

|                  | Data Compare Unit                            | 84 |  |

|                  | Using the Data Memory Editor                 | 85 |  |

| Generating Inter | rupts                                        | 87 |  |

|                  | Interrupt Capabilities of the Testcard       | 88 |  |

|                  | Asserting and Deasserting Interrupts         | 89 |  |

| Со | nte | ent | S |

|----|-----|-----|---|

|    |     |     |   |

| Using the Command Line Interface   | 91  |

|------------------------------------|-----|

| Starting the CLI                   | 92  |

| Basic CLI Command Syntax           | 93  |

| Using CLI Scripts                  | 94  |

| Bus Transaction Language Reference | 95  |

| BTL Commands                       | 95  |

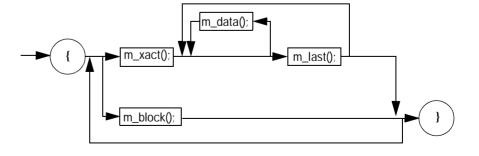

| m_block()                          | 96  |

| m_xact()                           | 97  |

| m_data()                           | 98  |

| m_last()                           | 99  |

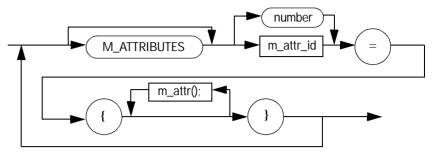

| m_attr()                           | 100 |

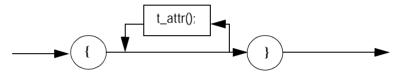

| t_attr()                           | 101 |

| BTL Command Parameters             | 102 |

| Block Transfer Parameters          | 103 |

| Address Phase Attributes           | 104 |

| Data Phase Attributes              | 105 |

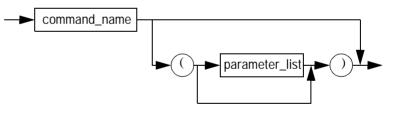

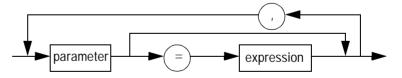

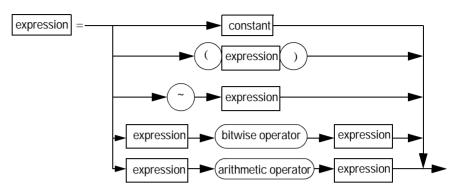

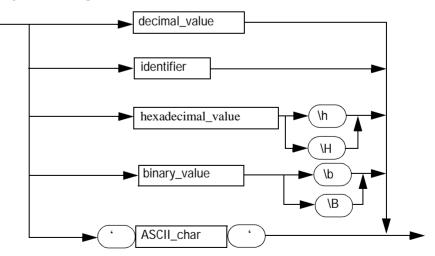

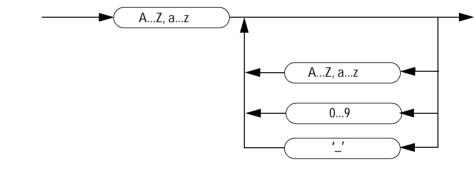

| BTL Syntax Diagrams                | 106 |

| Bus Commands                       | 106 |

| Parameters                         | 107 |

| Identifiers                        | 109 |

# **PCI Exerciser Overview**

Agilent's E2920 Verification Tools, PCI Series is your "window into the system" during product development, giving you access to almost all of the system components located on the PCI bus, as well as devices and adapters on secondary buses or within the system.

The PCI Exerciser (option #300) allows you to overcome the passive role in monitoring the PCI bus. With the PCI Exerciser, the testcard can be programmed to behave as a master and/or target device, and thus actively stimulate the bus.

For an overview of how you can use the Exerciser during the phases of the design cycle, refer to "Gaining an Active Part in Optimization and Validation" on page 8.

For an overview of the Exerciser's user interface, refer to "PCI Exerciser User Interface" on page 10.

*"PCI Exerciser Configurations" on page 12* shows examples of possible configurations for PCI Exerciser tests.

The major setup steps required are outlined in "Setting Up a PCI Exerciser Test" on page 14.

In most tests, the Exerciser will act as a master device and/or a target device on the PCI bus, initiating or serving transactions respectively. *"What is a Transaction?" on page 14* introduces this basic term.

This not only saves you the tedious chore of having to test your device with various other PCI components one after the other, but also allows you to test in a repeatable way, which means that you can reproduce any errors for deeper investigation.

You can also run functional tests, directing the Exerciser to generate and transmit large blocks of data in specified time intervals, thus testing how much PCI traffic your device can handle.

Validate Phase Validating your PCI device means ensuring its reliability in the long run. This means ensuring that it is stable under any application conditions, with any combination of plug-ins and any kind of traffic on the bus.

Using the PCI Exerciser as a master or a target device, you can test your design, repeatedly and consistently from the earliest opportunity, even during early bring-up and integration before a complete system is available.

In combination with the System Validation Package and/or the C-API/PPR options, the Exerciser offers fully controllable system-test, with wide coverage, reproducibility, and root-cause-analysis capabilities that will reveal system critical problems faster than any hot mock-up testing could.

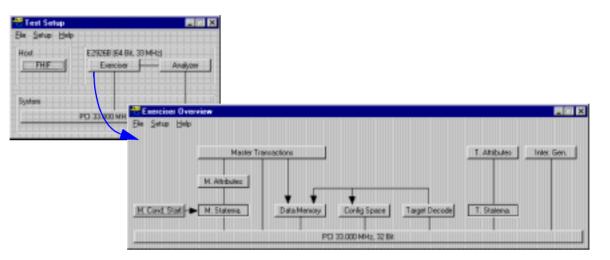

## **PCI Exerciser User Interface**

With the Agilent PCI Exerciser Graphical User Interface you can access and control all features of the Agilent E2925B testcard's Exerciser.

Clicking the *Exerciser* button in the Test Setup window or selecting *Show Exerciser Overview* from the *Exerciser* menu in the main window shows the Exerciser Overview window. Button, menu and the overview window are only available if the PCI Exerciser option has been installed.

The Exerciser Overview window shows the individual components of the PCI Exerciser, how they interact, and how they act on the bus. Clicking the buttons brings up the respective setup windows.

The Agilent E2925B testcard can act as a master or a target device on the PCI bus. Thus, the Exerciser mainly consists of the two parts master and target. Both are implemented with state machines, that are generated when compiling the input scripts.

For the master you can specify

- the master transactions to be performed,

- the protocol attributes to be used with the transactions,

- the data to be used for the transactions,

- the start conditions that need to be fulfilled before the transactions are started,

- whether or not errors should be injected during the transaction.

For the target you can specify

- which addresses are to be decoded (target decoders and configuration space),

- how received data is to be handled,

- the data to be transferred on request,

- the protocol attributes to be used during transactions,

- the decode speed,

- whether or not errors should be injected during the transaction.

Furthermore, you have full control on the testcard's **configuration space**. This means, you can program every register of the configuration space header to adapt your testcard to any test requirement.

Finally, the Agilent E2925B testcard is able to generate the **PCI interrupts** INTA# ... INTD# and any combination of them.

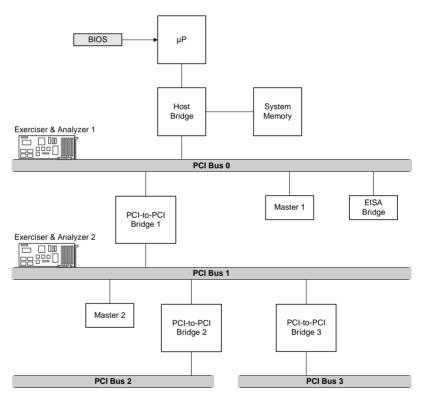

## **PCI Exerciser Configurations**

The configuration possibilities provided by the testcard and the GUI are basically the same as described for the Analyzer in the *Agilent E2925B PCI Analyzer User's Guide*.

When using the Exerciser, it depends on your testing requirements where you plug the testcard into the system under test. The following figure shows an overview of a typical computer system with two testcards plugged in.

You can use the Exerciser's master and target features to test each individual device—or the system as a whole:

Testing devices

The testcard's master can be used to initiate transactions to a target device under test. The testcard's target can be used to react to transactions initiated by a master device under test. Master devices can also be bridges, such as host bridges or PCI-to-PCI bridges.

The testcard can also be used for functional tests. For example, when testing communication devices (LAN cards, ATM cards), the testcard can be set up to generate and receive data blocks at specified data rates, thus allowing to test device and system behavior under full load.

• Testing a PCI-to-PCI bridge

To test the interfaces of a PCI-to-PCI bridge, testcards can communicate with other devices (or testcards) over the bridge or within one bus. Thus, you can test whether the bridge forwards transactions to the correct bus.

During start-up you can test whether configuration cycles are transferred correctly.

Testing a system

When testing a system as a whole, the Exerciser can be used to

- set up any PCI traffic scenario quickly and in a repeatable way

- simulate PCI devices that are not yet available

- generate interrupts to test the system's interrupt processing capabilities

## Setting Up a PCI Exerciser Test

Setting up a PCI Exerciser test includes the same steps as described for the PCI Analyzer:

- Inserting the testcard.

- Connecting to the testcard.

Additionally, you have to set up the Exerciser as required for your test. This is described in detail in

- "The PCI Exerciser as a Master Device" on page 31

- "The PCI Exerciser as a Target Device" on page 53

- "Using the Data Memory" on page 81

## What is a Transaction?

On every PCI system the different devices communicate via the PCI bus. This communication is controlled by the bus arbiter that determines which device may actively use the bus at any given time. This mechanism is used to avoid data collision and possible hardware damage. Basically, there are two different types of devices that operate on the bus: **masters** (actors) and **targets** (reactors).

The Agilent E2925B PCI Exerciser testcard can simulate either a master or a target device or both at the same time. This enables the testcard to emulate and/or test any device in your system under test.

The transfer of data between a master and a target device is performed in one or more data transactions. These transactions are initiated and controlled by the master, while the target reacts depending on the type of transaction. Every successful transaction includes the following steps:

- 1. The master requests bus access from the bus arbiter.

- 2. The arbiter grants the master to use the bus for a transaction.

- 3. The master starts the transaction by driving the address of the target and the bus command on the bus.

- 4. The target that owns the corresponding address range responds by asserting the DEVSEL# signal.

- 5. The master drives one or more data phases on the bus. If the command was a write command, the master also sends the data. Otherwise, the data is sent by the target.

- 6. When reaching the last data phase of the transaction, the master deasserts the FRAME# signal to indicate that it is ready to complete the transaction.

# Running A Sample PCI Exerciser Session

The following application examples explain how the testcard can be used in various tests. After introducing the major scenarios for the PCI Exerciser and showing how to prepare for the sample sessions, you will be guided through the following examples:

- "Guided Tour: Generating Master Transactions" on page 20

- "Guided Tour: Specifying Custom Target Behavior" on page 24

- "Guided Tour: Accessing VGA Frame Buffer Memory" on page 27

- **NOTE** The examples given here are also part of the *Agilent E2920 Software Demo guide*. If you have already worked through this guide, you may skip them here.

## **Example Scenarios**

The Agilent E2925B PCI Exerciser and Analyzer testcard can be used for basically any test that might be required, when developing devices, chipsets, or drivers for the PCI environment. Here you can find three examples that give a guided introduction to some of the main features of the testcard and its Graphical User Interface (GUI).

Testing a Target Device Imagine that you are integrating a PCI chip into an adapter or system. Or that your validation team (or even customer) reports that your PCI chip or system is not working properly under certain circumstances. Then you probably need to generate or reproduce a given PCI scenario and find out how your chip behaves in the real environment on certain PCI commands, on certain protocol variations like master wait states, or on error conditions such as wrong parity.

|                                      | In a case like this you can set up the Agilent PCI testcard as a master to access your chip or system under test with certain commands or attributes. This is explained in "Guided Tour: Generating Master Transactions" on page 20.                                                                                                                                                                                                                                                                          |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Testing a Master Device              | If you are developing, debugging, validating, or characterizing a PCI bus mastering device, you need a programmable target that can react deterministically in the required fashion. The Agilent PCI Exerciser provides this functionality. It has a 512-KB data memory that can be accessed with either memory or I/O transactions. The target protocol behavior is fully programmable for every individual data phase. This includes the number of wait states, the termination type, error insertion, etc. |

|                                      | An example, in which the Exerciser is set up as a target, is found in <i>"Guided Tour: Specifying Custom Target Behavior" on page 24.</i>                                                                                                                                                                                                                                                                                                                                                                     |

| Performing C Function Calls Directly | Besides the Graphical User Interface, the Agilent E2925B testcard also<br>features a C Application Programming Interface (option #320), providing<br>full access to all functions of the card.                                                                                                                                                                                                                                                                                                                |

|                                      | If you do not have the API installed or do not want to write complete C programs, you can use the Command Line Interface (CLI) instead, which is part of the GUI. With the CLI you can run scripts written in a simple script language.                                                                                                                                                                                                                                                                       |

|                                      | An example how this is done is presented in "Guided Tour: Accessing VGA Frame Buffer Memory" on page 27.                                                                                                                                                                                                                                                                                                                                                                                                      |

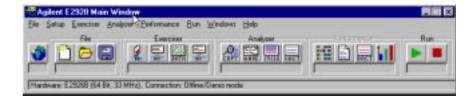

## Preparing for the Guided Tour

The first two examples described in the guided tours are designed to be performed in Offline/Demo Mode—without any hardware required. For the third example the GUI actually needs to be connected to a hardware. Otherwise, communication with the functions on the testcard, of course, cannot work.

All the setup files (\*.bst) and PCI signal waveform files (\*.wfm) that are mentioned in the following text are found in

<your\_installation\_directory>\samples\demo. If you did not change the

default setting during installation, <your\_installation\_directory> will be

C:\Program Files\Agilent\E2920 PCI Series <release\_number>.

**NOTE** The examples in the guided tours use an Agilent E2926B (64 bit, 33 MHz) testcard, but also apply to all other testcards of the Agilent E2920 series.

To prepare for the examples:

- 1 Launch the Agilent E2920 software.

- 2 From the Setup menu, choose Testcard Configuration.

- 3 In the Testcard Configuration dialog box, select the *Offline/Demo Mode* radio button.

| istcard Configuration                                                     | •              |                                                                          |            |

|---------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------|------------|

| w' <u>E</u> on≜g <u>H</u> ele                                             | Reds           |                                                                          | οĸ         |

| C PCI BUS                                                                 | /Slot 0.0000   | PCI Browne.                                                              | Cancel     |

| C 85232                                                                   | CON 2          | × \$7900 ×                                                               | Lance      |

| C Parallel                                                                | UPT 2          | *                                                                        |            |

| C Fact Host Interfact                                                     | . 0            | •                                                                        | Scan Parts |

| @ Offine/Denso Mos                                                        |                |                                                                          | Pire       |

| E 23268 164 84, 33 M                                                      |                | cted Testcard                                                            | 1          |

| Location<br>C Testoard in Host                                            |                |                                                                          |            |

| F Testoard compl                                                          | led remotely   |                                                                          |            |

|                                                                           |                |                                                                          |            |

| Support / Licensing<br>IF E2970A PO /<br>IF E2971A PO P<br>IF E2972A PO P | and the second | NOTES<br>Briefed Unsupporte<br>Drecked Licensed<br>Diffine/Denio mode: I |            |

4 Now choose *E2926B (64 bit, 33 MHz)* from the *User Selected Testcard* selection list, and check all license boxes in the *Support/Licensing* group.

Your display should now look like the window shown above.

5 Click *OK* and the main window should look like this.

You are now ready to start the guided tours.

## Guided Tour: Generating Master Transactions

This example shows how to set up the testcard as a master device that initiates data transfers on the PCI bus. More specifically, it generates burst transfers into the VGA frame buffer memory while varying certain protocol parameters.

## Loading the Setup Files

If you actually were connected to a testcard and your system ran in DOS mode, the results of this test could be viewed on the screen. Because we are in offline mode, start by loading the required files:

- 1 Load the setup file for this example (vga4.bst) by selecting *Load* from the *File* menu in the main window.

- **2** Load the PCI signal waveform file for this example (vga4.wfm) by selecting *Load from file* from the *File* menu in the Waveform Viewer window.

#### Setting up a Master Transaction

Once you have loaded the setup file and the waveform file, continue by setting up the master transaction for the test.

1 Open the Master Transactions window by clicking the Master Transactions button in the main window or by selecting the *Master Transactions* item in the *Exerciser* menu.

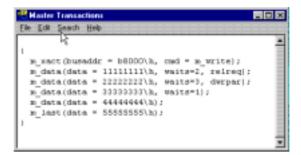

In the editor window you see that the master transactions for this test already are displayed. They are stored with all other settings in the setup file (vga4.bst).

The transaction blocks can be identified by the curly braces at the beginning and the end of each block. There is one transaction block specified for this test, which generates a memory write transaction to address b8000\h. The transaction performs a continuous burst of 5 dwords (unless the target—in this case the graphics card—disconnects earlier). The m\_data and m\_last statements specify the data to be transferred, along with optional protocol attributes such as wait states, wrong parity, release REQ#.

### Specifying a Conditional Start

When the Run button is clicked in the main window, the software writes the specified master transactions into the testcard's internal memory and starts execution either immediately or after a conditional start pattern has occurred on the bus. For this example, use a **conditional start pattern**.

1 Open the Master Conditional Start dialog box by selecting the *Master Cond. Start* item from the *Exerciser* menu.

| elp        |                                                                       |        |

|------------|-----------------------------------------------------------------------|--------|

| C Innediat | Master Start                                                          | ОK     |

| @ Pattern  | AD32-b8wa/h1& add_phase-1                                             | Cancel |

|            | Wait after pattern seen     F Na     Cockdelar     10     Dock Cycles |        |

In this dialog box the pattern is set to start the transactions after an access to the address range b8000\h...b8fff\h is done. This is coded in the boolean expression next to the *Pattern* radio button. To start the master transactions, both the value of the AD32 bit vector must be b8xxx\h and it must be an address phase at the same time.

The conditional start feature of the Agilent PCI Exerciser allows synchronization of traffic generation to start when the pattern appears either on the PCI bus or on any of the 12 external input ports of the testcard.

If you actually were connected to a testcard, you could start the test by clicking the Run button in the main window or by choosing *Run* from the *Exerciser* menu.

### **Viewing the Results**

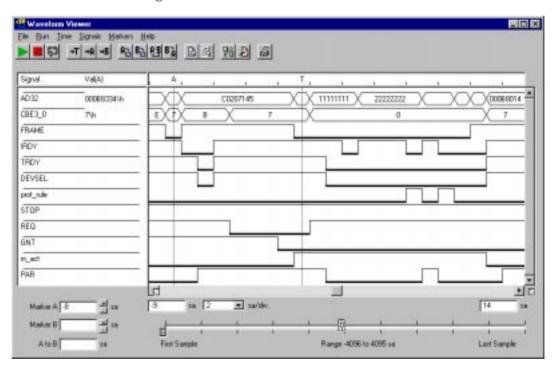

Use the Analyzer's Waveform Viewer to inspect the results of this test. The waveforms were loaded from the waveform file vga4.wfm.

1 Click the Waveform Viewer button in the main window (or use the *Waveform Lister* item from the Analyzer menu) to open the waveform viewer.

In the following screenshot you see the section of the waveform diagram in which the transaction block was executed.

Note the transaction that triggers the start of the Exerciser (shown at marker A). It is also easy to identify the transaction block during which the master is active (m\_act is high from the trigger point T on; it is always high while the testcard's master is active). During this time the AD32 signal first holds the target address (address phase) and then the transferred data in the five data phases.

To see the corresponding section of the Bus Cycle Lister window:

2 Click the Bus Cycle Lister button in the main window (or use the *Bus Cycle Lister* item from the Analyzer menu) to open the bus cycle lister.

| Ellus Cycle  <br>File : Bus : Sec | Lister<br>with Heb                                             | -02    |

|-----------------------------------|----------------------------------------------------------------|--------|

| -                                 | -1 [93] @ Gence                                                |        |

| -9:                               | 30.3ns IDLE                                                    |        |

| -81                               | 30.3ns Memory Mrite & = 000b8334                               |        |

| -7;                               | 30.3ns WAIT (no DEVSEL#)                                       |        |

| -6:                               | 30.3ns D = c0207145 BE = 1011                                  |        |

| -61                               | 30.3ns IDLE                                                    |        |

| -9:                               | 30.3ns IDLE REQ#                                               |        |

| =81                               | 30.3ns IDLE REQN                                               |        |

| -21                               | 30.3ns IDLE REQ#                                               |        |

| -1:                               | 30.3 ns IDLE REQU GNTS                                         |        |

| 01                                | 30.3ns * Hemory Write A = 00008000 REC# GNT#                   |        |

| 1:                                | 30.3ns * WAIT (no DEVSEL#, no IRDY#) GNT#                      |        |

| 21                                | 30.3ns * WAIT (no IRDY#) ONT#                                  |        |

| 23                                | 30.3ns * D = 11111111 BE = 0000 GNT#                           |        |

| 4:                                | 30.3 n# * WAIT (no IRDY#) GNT#                                 |        |

| 51                                | 30.3ns * WAIT (mo IRDY#) GNT#                                  |        |

| 6:                                | 30.3ns * WAIT (no IRDY#) GNT#                                  |        |

| 7:                                | 30.3ns * D = 22222222 BE = 0000 ONT# Protocol Error PARITY 3 B | PARITY |

| 0:                                | 30.3ns * WAIT (no IRDY#) GNT#                                  |        |

| 9:                                | 30.3ns * D = 33333333 BE = 0000 GNT# Protocol Error            |        |

| 101                               | 30.3ns * 0 = 44444444 SE = 0000 087#                           |        |

| 11:                               | 30.3ns * D = 55555555 BE = 0000 GNT#                           |        |

| 12:                               | 30.3ng IDLE ONT#                                               |        |

Note that two protocol violations are indicated. If the tool was connected to an actual testcard, examining the Protocol Check window would reveal that the second protocol violation indicates that a parity error occurred but was not signaled by the receiver of the data.

When larger amounts of data need to be transferred, an alternate syntax allows you to generate bursts of virtually any length (subject to the target's behavior). To see an example of the syntax select *New* from the *File* menu in the Master Transactions editor window.

There, the second transaction block, commented out though, shows how to specify the number of dwords to transfer (nod=2) within a block transfer. Additionally, you can assign an attribute page to each transaction block, which defines further protocol attributes for the master. These attribute pages are found in the Master Attributes editor window accessible via the *Master Attributes* item in the *Exerciser* menu of the main window.

# Guided Tour: Specifying Custom Target Behavior

This example illustrates how to set up your Agilent PCI testcard as a target device. The behavior of the target is fully programmable. This includes the address ranges that are decoded, how received data is handled, which data is transferred on request, and the protocol attributes that are used during the transactions.

## Loading the Setup Files

If you actually were connected to a testcard and your system ran in DOS mode, the results of this test could be viewed on the screen. Because we are in offline mode, start by loading the required files:

- 1 Load the setup file for this example (target1.bst) by selecting *Load* from the *File* menu in the main window.

- **2** Load the PCI signal waveform file for this example (target1.wfm) by selecting *Load from file* from the *File* menu in the Waveform Viewer window.

## Setting up the Target Decoders

For this guided tour, we will only view the prepared target decoder setups.

1 To view the setup for the target decoders, choose the *Target Decode* item from the *Exerciser* menu.

|              |          |            | Reidhanica | Wile PU to | www.     | eger) |

|--------------|----------|------------|------------|------------|----------|-------|

|              | Conlig   | EWR 0-LO   | BAR 0-H    | BAR 2      | BAR 3    |       |

| Ervable      | Enabled  | Enabled    | see left   | Enabled    | Disabled | ŀ     |

| Speed        | slow     | redun      | see iel1   | redun      | nedum    |       |

| Resource     | 68/3     | data       | see left   | dələ       | dələ     |       |

| Res. Base    | 0.0      | Dh         | see left   | 40000\/h   | 0%h      |       |

| Res. Size    | 512Kbyte | 256Kbyte   | see iel1   | 128 byte   | 4Rbyte   |       |

| Base Addr.   | 0x0      | Dwidd00000 | Dw0        | Owdc00     | 0+0      |       |

| Size         | 256 byte | 512Kbyte   | see left   | 128 byte   | Disabled |       |

| Location     |          | space64    | see left   | ю          | 1pace32  |       |

| Prefetchable |          | No         | see left   |            | No       |       |

| Behavior     |          | normal     | see left   | nomal      | nomal    |       |

| Delault      | Default  | Default    | Detault    | Delault    | Delault  |       |

|              | •        |            | · ·        | 1          |          | ъſ    |

In Offline/Demo Mode the Target Decode window will look slightly different than the screenshot below.

Base Address Registers

The content of the Target Decode window mainly is an interpretation of the configuration space settings. In the figure above you see that two standard decoders together are set up to decode 64-bit addresses. The two columns representing them are titled *BAR 0-LO* and *BAR 0-HI*, where the abbreviation BAR stands for base address register. The address space type and location are set in the location field of the respective decoder.

Internal Resources The three rows *Resource*, *Res. Base*, *Res. Size* determine to which internal data resource the decoders are connected to. These settings define how the received data is to be handled or which data is to be sent on request.

#### **Specifying the Target Protocol Behavior**

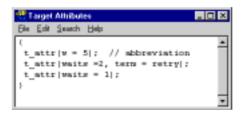

The target protocol behavior is defined in a similar way to that of the master behavior.

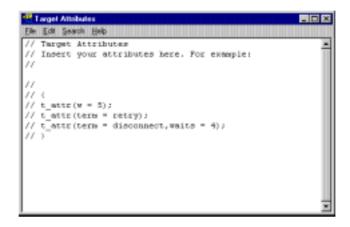

1 To inspect the protocol attributes, open the Target Attributes editor window by selecting the *Target Attributes* item in the *Exerciser* menu.

These attributes specify what happens when the testcard's target is accessed by a master.

#### **Viewing the Results**

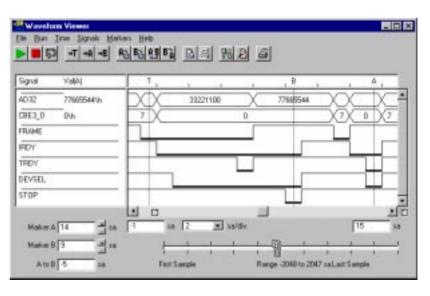

Compare the settings made in the previous step with the traffic captured on the bus.

1 Click the Waveform Viewer button in the main window (or use the *Waveform Lister* item from the Analyzer menu) to open the waveform viewer.

Notice that the PCI Exerciser target behaves exactly as it was set up:

- The first data phase has 5 wait states (after the triggerpoint T).

- The second data phase does not complete until it is retried once.

Marker B shows the retry and Marker A shows the completed data transfer. This behavior can also very easily be observed in the transaction lister.

**NOTE** The t\_act signal—not shown on the screenshot—is always high while the testcard's target is active.

## Guided Tour: Accessing VGA Frame Buffer Memory

In this example, the Agilent PCI testcard is used to poke some data values directly into the video frame buffer memory of a VGA graphics adapter. If you are working interactively, the testcard's Command Line Interface is a very easy way to use these host access functions.

The Command Line Interface uses the CLI equivalents to the functions provided by the C-API (option #320) described in detail in the *Agilent E2925B C-API/PPR Reference*.

#### Starting the Command Line Interface

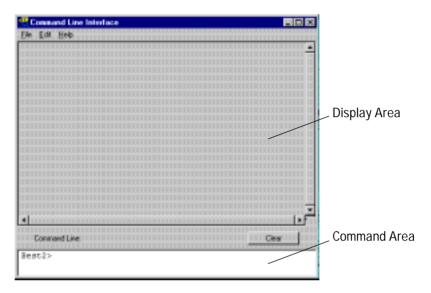

To open the command line interface:

1 Select Command Line Interface from the Windows menu.

This opens the Command Line Interface window:

| Command Line Interface | _ D × |

|------------------------|-------|

| Ele Edit Help          |       |

|                        | •     |

|                        |       |

|                        |       |

|                        |       |

|                        |       |

|                        |       |

|                        |       |

|                        |       |

|                        |       |

|                        |       |

|                        |       |

|                        |       |

|                        |       |

| -                      |       |

|                        |       |

| Command Line           | Cear  |

| Best2>                 |       |

|                        |       |

|                        |       |

## **Entering the Required CLI Commands**

With the use of the Command Line Interface a character will be written into the top left corner of the VGA text screen (visible in DOS mode only). This is done by writing a single byte to the physical memory address 0xb8000. Then the cursor is set next to this character by doing two I/O word writes to I/O address 0x3d4. See the following screenshot.

| Command Line Interface                                                |

|-----------------------------------------------------------------------|

| Elle Edit Help                                                        |

| SestNostPCIRegSet space-men Bus_addr=b8000\h size=1 val=41\h<br>Ready |

| BestHostPCIRegSet space-io Bus_addr=3d4\h size=2 val=DOOe\h<br>Ready  |

| SestBostPCIRegSet space=io Bus_addr=3d4\h size=2 val=010f\h<br>Ready  |

| 4 DE                                                                  |

| Conward Line. Clear                                                   |

| Sest2>                                                                |

Call three commands were typed in at the *Best2*> prompt. The commands are displayed along with the results in the output area of this window. In this case no specific output was returned by the testcard. Hence, only *ready* is displayed to indicate successful completion of the command.

When the Agilent E2920 software is running in demo mode, no connection to a testcard is established. Thus, typing commands in the command line interface window has, of course, no effect, and generates a reply:

#### $B\_E\_ERROR$ : Error transferring command (1).

With the command line interface you can also log and run CLI scripts. Hence, you do not need to type all commands by hand for every test. The option providing full flexibility and control on your system is available with the C Application Programmer's Interface (C-API) which is the Option #320 to your testcard. With the C-API you can implement your own C programs that may access all functions of the testcard.

# The PCI Exerciser as a Master Device

|                          | The Exerciser of your Agilent E2925B testcard can simulate any device<br>on the PCI bus under test. There are mainly two different types of<br>devices—masters and targets. Other devices (for example, network<br>interface cards) have both master and target functionality.                                                                                                                                                                          |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | The Exerciser contains both a master and a target along with a few other components. All necessary information about the testcard's <b>master device</b> is provided here.                                                                                                                                                                                                                                                                              |

| Programming Transactions | A device on a PCI bus is called a master if it requests to access the bus<br>and performs data transfers when the bus is granted to it. A data transfer<br>consists of one or more transactions. Information on the programming of<br><b>master transactions</b> and their <b>properties</b> is found in <i>"Programming<br/>Master Transactions" on page 32</i> .                                                                                      |

| Master Attributes        | Additionally, the Agilent PCI Exerciser allows to control the protocol<br>behavior of its master device. These protocol <b>attributes</b> normally do not<br>have any effect on the result of a transaction. They only determine the<br>master's behavior in terms of inserted delays of different types,<br>transaction terminations, and more. How to program these attributes is<br>described in <i>"Controlling Master Attributes" on page 40</i> . |

| Run Options              | After the master device is set up completely, you can run it with several options. These are explained in <i>"Running the Master" on page 47</i> .                                                                                                                                                                                                                                                                                                      |

\_\_\_\_

## Programming Master Transactions

In order to set up the Agilent PCI Exerciser as a master, you need to specify **master transactions**. After the master is started, it will perform these transactions on the bus. For this purpose it requests from the PCI bus arbiter to use the bus. When the bus is granted to the master, it initiates the data transfers on the bus. For more details, refer to "*Master Transactions Overview*" on page 33.

For each transaction, you can specify **transaction properties** like bus command or bus address (see *"Transaction Properties" on page 36*) valid for the whole transaction.

**NOTE** These transaction definitions basically define *what* is to be done by the master, that is, they specify the data that is to be transferred from one location to the other. On the other hand, the **master attributes** specify how the transaction is to be performed (see *"Controlling Master Attributes" on page 40*).

For specifying transactions and properties, the Agilent PCI Exerciser provides a master transaction editor. The editor uses the **Bus Transaction Language (BTL)** as input format for the transactions. BTL descriptions for transactions may, for example, look like this:

```

{

m_xact(busaddr = b8000\h, cmd = mem_write);

m_data(data = 8f458f42\h, waits = 3);

m_last(data = 8f548f53\h);

}

...

{

m_block(busaddr = b8008\h, cmd = mem_write, intaddr = 0\h,

nofdwords = 20, attrpage = mypage);

}

```

A complete list of the commands and parameters of the Bus Transaction Language is found in *"Bus Transaction Language Reference"* on page 95.

#### **Master Transactions Overview**

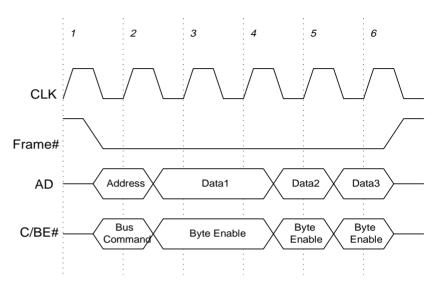

The figure shows a typical transaction, consisting of one address phase and one or more data phases.

According to the number of data phases, two transaction types can be distinguished: **single transactions** and **block transactions** (see *"Single Transactions and Block Transactions" on page 34*).

For your master transactions, you can specify any combination of single transactions and block transactions.

#### Address Phases and Data Phases

Address Phases In the address phase the master asserts the FRAME# signal and drives the address of the target device on the bus along with the bus command. All target devices on the bus latch and decode the address. The target that finds this address in its own address range, replies with a device select DEVSEL# signal.

The bus commands typically are of one of the following types. The respective command in BTL syntax is given in parentheses:

- memory read or write (mem\_read, mem\_write),

- I/O read or write (io\_read, io\_write),

- configuration read or write (config\_read, config\_write),

- memory read line (mem\_readline),

- memory read multiple (mem\_readmultiple),

- memory write invalidate (writeinvalidate),

- interrupt acknowledge (int\_ack),

- special cycle (special),

- reserved cycle (reserved\_4, reserved\_5, reserved\_8, reserved\_9).

- **Data Phases** After the addressed target signaled that it is ready for the transaction (by asserting TRDY#), the first data phase takes place. In the data phases the data is transferred. If the bus command was a write command, the data is sent by the master. In case of a read command, the data is sent by the target.

There can be more than one data phase in a transaction. Transactions with several data phases are commonly referred to as bursts. The way in which a transaction is eventually performed depends also on the protocol and the device properties.

#### Single Transactions and Block Transactions

According to the number of data phases, there are two different types of transactions:

- Single transactions

- Block transactions

- Single Transactions This type of transaction uses one BTL command per transaction phase. Use this type if you want to specify the transfer data directly in your editor. Also, you can define your master attributes for every individual transaction phase within the BTL commands.

The available BTL commands are:

- m\_xact(). This command initiates a new transaction by driving an address phase onto the bus.

- m\_data(). This command follows m\_xact(). It performs a data phase on the PCI bus that is not the last or only data phase of the burst.

- m\_last(). This command performs a data phase that is either the last or the only data phase of a burst.

In the following example, the first line starts the transaction and specifies the transaction properties (busaddr, cmd). The next two lines perform the data phases and specify some master attributes (data, waits) for each phase.

```

{

m_xact(busaddr = b8000\h, cmd = mem_write);

m_data(data = 8f458f42\h, waits = 3);

m_last(data = 8f548f53\h);

}

```

**Block Transactions** When using a block transaction with m\_block(), you can define the transfer of a larger amount of data within one BTL command. This data must be stored in the internal data memory and you need to specify the internal start address of this data.

The master then performs one burst containing the complete data unless master termination is specified by a master attribute, or the burst is terminated by a participating device or an error. In that case, the master initiates a new transaction and continues transferring the data from where it was stopped.

The master attributes for the individual phases of the block transfers cannot be specified in the editor. But you can assign an attribute page to each block transfer, that is worked through line by line for the transaction phases. This is an example for a block transaction:

```

{

m_block(busaddr = b8008\h, cmd = mem_write, intaddr = 0\h,

nofdwords = 20, attrpage = mypage);

}

```

#### **Transaction Properties**

The commands of the Bus Transaction Language can be used with different properties. These transaction properties more specifically describe the master behavior. They always apply to all phases of a transaction. Hence, they are defined in the first command of the transaction, either m\_block() or m\_xact().

The transaction properties are stored in the master block transfer memory on the testcard and are thus also referred to as the master block properties. They hold parameters like the bus command and the addresses from and to where data is to be sent. Some of these properties are strictly required, others use default values when omitted.

According to their contents, two types of properties can be distinguished:

- "Properties Containing Values" on page 36

- "Properties Containing Pointers" on page 37

These properties hold pointers to other memories and thus control the co-operation between these memories on the testcard.

#### **Properties Containing Values**

The following list summarizes and briefly explains the available master block properties containing explicit values. The respective BTL parameter is put in parentheses.

• Bus Command (cmd).

This property is always required and specifies the PCI bus command used for the transaction. The possible choices are memory read or write, I/O read or write, configuration read or write, memory read line, memory read multiple, and memory write invalidate. Beside of that, you can also drive interrupt acknowledge, reserved or special cycles on the bus.

• Dual Address Cycle, DAC (busdac).

This flag is optional. It determines whether a 32-bit single address phase or a 64-bit dual address phase is performed.

• Bus Address (busaddr, busaddr\_hi).

The bus address also is required for every transaction. It can be 32 or 64 bits, depending on the dual address cycle flag and the bus command. To transfer 64-bit addresses, Dual Address Cycle (DAC) must be enabled. Certain bus commands require aligned PCI bus addresses, for example memory write invalidate.

• Number of Dwords (nofdwords).

This property is required for block transactions using m\_block(). It specifies the amount of data that is transferred by the master. This means the number of data phases that are implemented, because you can send one dword (4 bytes) per data phase. Note, that the actual amount of transferred data might be less, due to byte enable settings or misaligned addresses.

• Compare Flag (compflag, compoffs).

If the optional compare flag is set, data read from another device is not stored in the testcard's data memory but is compared to previously stored data. The parameter compoffs (compare offset) holds the address that determines to which reference data the comparison is done. If a data mismatch occurs, a compare error is reported.

• Continue With Attributes (contattr).

This property determines whether the master attribute page is restarted at the beginning of a new transaction (default). Use longer attribute pages and set this flag to "1" to generate transactions with a greater variety of protocol attributes.

• Conditional Start (condstart).

Setting this flag will cause the master to pause until a specified event occurs on the bus or on one of the trigger I/O ports.

Note, that flag is only evaluated if the pattern that is used for detecting this event has been programmed with the Command Line Interface (CLI). This flag has no effect if the conditional start run mode is selected as described in *"Specifying a Start Condition"* on page 48.

#### **Properties Containing Pointers**

The following three properties are also stored in the master block transfer memory, but they merely hold pointers to other memories. They control the co-operation of the different types of memories during the master run.

These pointers always point to a start value in the respective destination memory. If enabled, an internal pointer moves on from this entry point one line per successfully completed data phase. Thus, the pointer values in the master block transfer memory remain unchanged. • Attribute Page (attrpage).

This parameter is optionally available for m\_block() transactions. It is stored as a pointer to an attribute page. An attribute page contains a sequence of attribute lines m\_attr() in the attribute memory. With this property, arbitrary protocol attributes can be assigned to every phase of the transaction.

See also "Controlling Master Attributes" on page 40.

• Byte Enable Control (byten, byten\_var).

With the parameter byten, you can define fixed byte enable values for a transaction (assuming byten\_var has its default value 0). Using byten\_var=1 instead will cause the byte enable memory pointer to be incremented with every successfully completed data phase.

Use the Command Line Interface (CLI) to store sequences of byte enable values in the byte enable memory. See "Using the Command Line Interface" on page 91 for details.

• Internal Address (intaddr).

This property is required for m\_block(). This address points to the testcard's internal data memory. During write transactions, the data stored in this memory is sent to the target. In read transactions, the received data is stored here. When doing a data compare (compare flag set), this address does not have any effect. The address of the compare data is stored in compoffs.

See also "Using the Data Memory" on page 81.

For more detailed information on the participating memories and registers on the testcard, please refer to the *Agilent E2925B Programmer's Guide*.

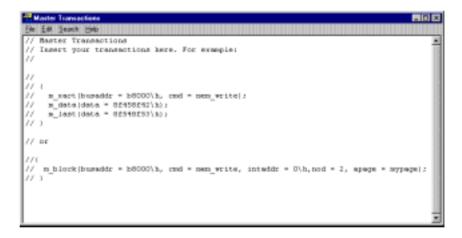

## **Implementing Master Transaction Scripts**

The setup of the master transactions is implemented in transaction scripts. These scripts use the Bus Transaction Language (BTL) and are entered into the master transaction editor. This editor is opened by clicking the Master Transactions button or by selecting the *Master Transactions* item from the *Exerciser* menu in the main window.

Bus Transaction LanguageThe Bus Transaction Language is a simple script language allowing you<br/>to easily set up PCI bus transactions in the Agilent Graphical User<br/>Interface (GUI). A BTL script consists of a sequence of commands and<br/>their parameters.

**Example** The following screenshot shows a simple example script, containing two transactions, commented out though. To load this example into your editor, select the *New* item from the *File* menu.

Both transactions perform a memory write command to address b8000\h (VGA memory):

- The first transaction consists of three commands, one for each phase. Note that the data is specified within the data phase commands.

- The second transaction is implemented with the block transfer command m\_block(). Here the data is taken from the data memory at internal address 0\h. There is also an attribute page mypage assigned to the transaction.

Your scripts will be saved together with the setup in the .bst file. You can also save the scripts individually, using the *File* menu of the transaction editor.

The other menus contain a few more editor functions that may help you editing the scripts.

# **Controlling Master Attributes**

While the transaction script defines *what* the master does, the master attributes allow you to specify *how* this is done.

More specifically, the **master attributes** describe all properties of a bus phase during a data transfer. Examples are the number of wait states the master inserts into a data phase, or whether a parity error should be signaled during an address phase, etc.

The behavior specified in the master attributes should not affect the result of the data transfer. Thus, you can repeat a test with the same master transaction settings but varying attribute settings and then compare the results.

Depending on the type of transaction used, the master attributes can either be specified in the transaction BTL commands directly, or in socalled attribute pages (see *"Specifying Master Attributes" on page 40*).

For the latter case, the Agilent PCI Exerciser provides a **master attribute editor** to set up additional parameters that define the protocol behavior of the master device (see "*Implementing Master Attribute Scripts*" on page 46).

The different types of master attributes are:

- "Master Address Phase Attributes" on page 42

- "Master Data Phase Attributes" on page 44

- "Master Control Attributes" on page 45

#### **Specifying Master Attributes**

According to the type of transaction, the master attributes can be specified in one of two ways:

- For single transactions they are specified as part of the BTL command (see "Attributes in BTL Commands" on page 41).

- For block transactions they are specified in attribute pages, which will be processed line by line for the phases of the block transfer (see *"Attribute Pages" on page 41*).

#### Attributes in BTL Commands

If you specify single transactions in the transaction editor (one command per transaction phase), the attributes are set up along with the commands. Normally, you will specify address phase attributes in address phase commands and data phase attributes in data phase commands. But you can also mix them up.

Consider the following special cases:

- Defining data phase attributes in the address phase command m\_xact() causes these attributes to be set as default values for the complete transaction. If this parameter then is set to another value in a data phase, all following data phases of this burst will still use the default value.

- On the other hand, address phase attributes that are specified in the data phase commands m\_data() and m\_last() will only come into effect when the transaction is terminated at this point by some reason, and you want to use different attributes for the new transaction starting at this point.

#### **Attribute Pages**

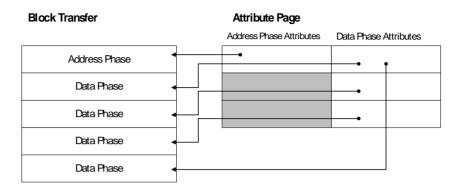

If you use block transactions, the attributes need to be defined in attribute pages in the master attributes editor window (see *"Implementing Master Attribute Scripts" on page 46*). And you can, optionally, assign one of these attribute pages to each block transaction.

When the master is running and performing a block transfer that has an attribute page assigned to it, the attribute lines  $(m_attr())$  in this page are processed line by line for the phases of the block transfer.

Basically, any attribute line can happen to be used for both address phases and data phases. This depends on the number of lines in the page, the length of the corresponding bursts, and the restart and repeat settings. The following figure shows how the address phase and data phase attributes are used in an attribute page consisting of three lines.

During a **data phase**, only the specified data phase attributes in the current attribute line will come into effect. All address phase attributes are ignored. The next transaction phase will then use the next attribute line.

During an **address phase**, the address phase attributes of the current attribute line are used. Then, during the first data phase of this burst, the data phase attributes of still the *same* attribute line are used. After that, the next transaction phase (no matter of which type) will use the next attribute line.

When reaching the end of the attribute page before completing the block transfer, it is restarted with the first attribute line (unless this default behavior is disabled).

#### Master Address Phase Attributes

The following list gives an overview of the available address phase attributes. The respective BTL parameter is put in parentheses.

• Try Fast-Back-to-Back (tryback).

Usually, there must be at least one idle cycle (turn-around cycle) between two transactions of the same master. However, if the master wants to perform two transactions, it does not need to deassert its REQ# signal, and if the arbiter leaves the bus to it, the master can skip the idle cycle(s) between the transactions. This is called "fast-back-to-back".

A number of conditions must be met for performing transactions fastback-to-back. Therefore, the master can only be set up to *try* a fastback-to-back transfer. Whether the fast-back-to-back transfer *really* can be performed depends on the conditions at runtime. For detailed information, please refer to the *Agilent E2925B C-API/PPR Reference*. • Delay, Exerciser Idle (delay).

If "Try Fast-Back-To-Back" is disabled, the Exerciser can stay idle after completion of a transaction before REQ# is asserted for the next transaction. Between blocks, the Exerciser always inserts a gap of at least 15 clocks.

Note, that the arbiter also can insert idle cycles between transactions.

• Lock (lock).

The LOCK# signal is used by a master to lock a target. This signal can only be used by one master at a time, in this case the Agilent PCI testcard. This device then has exclusive ownership of the target device until it unlocks it (that is, release LOCK#).

To test how the target behaves in this situation, the Exerciser can pretend to be two masters in one device. One master locks the target device, the "other" master tries to access the locked target.

• Wrong Parity Calculation (awrpar, dacwrpar).

The Exerciser provides attributes to set the parity bit PAR to the wrong value in the following situations:

- in the first (DAC) or only (32-bit address) address phase cycle of a 32-bit transaction (awrpar),

- in the second address phase cycle of a dual address cycle transaction (dacwrpar).

- System Error Signaling (aperr, dacperr).

The Exerciser can signal a system error in the following situations:

- for the first (DAC) or only (32-bit address) address phase cycle of a transaction (aperr),

- for the second address phase cycle of a dual address cycle transaction (dacperr).

In either case, the error is signaled with a two clock delay after the attribute is set. This is required by the PCI specification.

Note, that the master is actually asserting the parity error signal PERR. But a parity error during a data phase is considered as a system error and will cause SERR to be asserted, too. As a result, all targets should draw from the bus immediately.

System errors need to be enabled in configuration space. Otherwise, this attribute will not have any effect.

• Release Request (relreq).

Usually, the request signal REQ# is released one clock after the bus enters the idle state after a transfer. The Exerciser, however, can release the request signal any number of clocks after the end of the transaction's address phase. Such behavior can place a load on the arbiter.

• Resume Delay (resumedelay).

The Exerciser can insert a programmable number of clocks before it resumes after a target termination. This gives other masters a programmable chance to obtain the bus.

#### Master Data Phase Attributes

The following list gives an overview of the available data phase attributes.

• Waits (waits).

The Exerciser's master can insert up to 30 wait cycles into a data phase. On the bus, wait cycles are inserted by deasserting the initiator ready signal (IRDY#).

• Data (data, hi\_data).

The data attribute is used for the data phase commands m\_data() and m\_last(). Here the data is specified that is to be transferred.

• Marker (marker).

With this attribute you can set a marker to an integer value during a transaction phase. This number can then be used as input for pattern terms. Pattern terms are used for synchronization with other parts of the PCI testcard, for example, to trigger the trace memory of the Agilent PCI Analyzer.

• Wrong Parity Calculation (*dwrpar*).

In a data phase, the Exerciser can set the parity bit(s) to the wrong value only for write transfers, because in read transfers the parity is calculated by the target.

• Parity Error Signaling (dperr).

The master can set a parity error (PERR#) that will then be asserted with a delay of two clocks. If actually a parity error should occur on the bus concurrently, it will be ignored. However, this error will be recognized by the testcard's protocol rule observer and can be used to trigger the trace memory.

Parity errors need to be enabled in the configuration space. Otherwise, this attribute will not have any effect. • System Error Signaling (dserr).

The master can signal a system error during a data phase. System errors need to be enabled in the configuration space. Otherwise, this attribute will not have any effect.

• Release Request (drelreq).

Usually, the request signal REQ# is released one clock after the bus enters the idle state after a transfer. The Exerciser, however, can release the request signal any number of clocks after the beginning of the transaction's data phase. Such behavior would stress the arbiter.

The data phase release request instruction is ignored if the master has previously been instructed to release the request, for example, during the address phase or during a prior data phase of this transaction.

## Master Control Attributes

The control attributes are used to determine how the master steps through the master attribute memory. The following list describes the attributes that control this behavior. Control attributes are valid both for address phase and data phase attributes.

• Repeat (repeat).

Specifying the number of times a particular attribute line is repeated before switching to the next line. A line of attributes can be repeated up to 4 billion times  $(2^{32})$ .

• Burst Length.

The burst length is controlled via the last attribute, which indicates the last data phase of a burst and therefore the end of the transaction.

Regardless of this flag, a transaction will always be terminated if

- the target signals "retry", "disconnect", or "abort",

- the specified number of dwords has been completely transferred (see "*Programming Master Transactions*" on page 32).

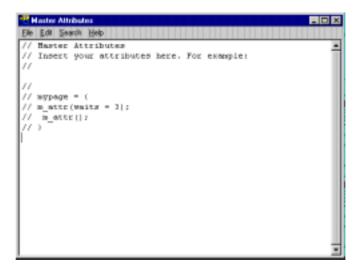

## **Implementing Master Attribute Scripts**

The Agilent PCI Exerciser provides a master attributes editor, which works similar to the master transaction editor.

The setup of the master attributes is implemented in attribute scripts. These scripts use the Bus Transaction Language (BTL) and are entered into the master attributes editor. This editor is opened by selecting the *Master Attributes* item from the *Exerciser* menu in the main window.

Bus Transaction LanguageThe Bus Transaction Language is a simple script language allowing you<br/>to easily set up PCI bus transactions and attributes in the Agilent<br/>Graphical User Interface (GUI). A BTL script consists of a sequence of<br/>commands and their parameters.

**Example** The following screenshot shows a simple example script, containing an attributes page mypage, commented out though. To load this example into your editor, select the *New* item from the *File* menu.

This attribute page contains two attribute lines that are defined with the command  $m_attr()$ . The first attribute line causes the master to insert three wait cycles into the first data phase. The second line will cause the master to use the default attributes for the following data phase. With no other settings the page will then be restarted, resulting in the master inserting three waits into every second data phase.

Your scripts will be saved together with the setup in the .bst file. You can also save the scripts individually, using the *File* menu of the transaction editor.

# **Running the Master**

When you have completely set up the master, you can prepare to run your test:

- You can exactly specify the conditions for starting and running the master (see "*Preparing Test Execution*" on page 47).

- Depending on these conditions, there are several ways to start the master (see "Starting the Master" on page 50).

- If required, you can stop the master manually (see "Stopping the Master" on page 51).

## **Preparing Test Execution**

You have several options how to run the test:

- You can start the test manually by means of the Run button or the *Start* item from the *Run* menu. You can use the Run Options to determine the testcard components to be started (see "*Setting up the Run Options*" on page 47).

- You can specify a start condition to start the master automatically after a certain event (see "Specifying a Start Condition" on page 48).

#### Setting up the Run Options

First of all, you need to decide whether you want to run your master alone or in combination with other parts of the Agilent E2925B testcard. These settings are made in the Run Options window:

1 In the main window select *Run Options* from the *Run* menu.

| <mark>문</mark> Run (<br>남아 | Options      |       | -        | ×   |

|----------------------------|--------------|-------|----------|-----|

|                            | Run-B        | ultor |          |     |

| C By                       | ni Analyzer  | 1     |          |     |

| E BR                       | o Feizur     |       |          |     |

| R Ru                       | ns Master    | P.    | Repetit  | ive |

| IT Re                      | spect Arbits | 8     |          |     |

| C Int                      | z Target     |       |          |     |

| IT Cle                     | an protoco   | l and | timing a | 100 |

| B                          | un 🗌         |       | Stop     |     |

2 Select the testcard components to be started when using the Run button or the *Start* item from the *Run* menu.

Only components that are enabled with your testcard can be selected.

#### **Specifying a Start Condition**

You can specify the following options for the start of the master:

- Immediate Start. This is the default option. After the master is started, it will immediately perform the specified transactions.

- Conditional Start. Alternatively, you can define a start condition. This is done with a start pattern that needs to occur either on the bus or on one of the I/O trigger ports.

- Fixed Delay. The third option is to define a fixed delay for the start. After the master is started, it waits for the specified number of clocks before it asserts REQ# to request GNT to start a transaction.

You can also set up a combination of the conditional start and the fixed delay. In this case the master first waits for the pattern event to occur. After this event has been detected, it waits the additional delay time before starting the transactions.

The detection of a pattern event is implemented with a boolean expression. If this expression turns true, the master starts running. The fixed delay is simply a number of clock cycles that you set in the GUI.

You can combine the two features or use only the conditional start or only the fixed delay start. For the latter case you set the boolean pattern expression to TRUE to make it switch immediately. Then the master only waits the fixed delay.

To set up a delayed start of either type, proceed as follows:

1 Select *Master Cond. Start* from the *Exerciser* menu in the main window.

| Haster Conditio<br>Help | nal Start                                                   |              |

|-------------------------|-------------------------------------------------------------|--------------|

| C Inmediat              | Mariler Stat<br>AD32-bBios/ih 82 add_phose=1 Edk.           | 0K<br>Cancel |

|                         | Wat alter pattern seen<br>F No<br>Clockdelav 10 Dack Cycles |              |

| Signal    | Value     | 1 <u>i</u> | UK    |

|-----------|-----------|------------|-------|

| AD64      | xmonomx\h | 1          | Cance |

| AD 32     | xmonom/h  |            | Dear  |

| CBE7_4    | xh        |            |       |

| CBE3_0    | xh        |            |       |

| FRAME     | ×         |            |       |

| RD'Y'     | ×         |            |       |

| TRDY'     | ×         |            |       |

| STOP      | ×         |            |       |

| DEVSEL    | ×         |            |       |

| RAR .     | ×         |            |       |

| add_phase | ×         |            |       |

| ADKS4     | ×         |            |       |

| REQ64     | ×         |            |       |

| PAR64     | ×         |            |       |

| RST       | ×         |            |       |

| LOOK      | ×         | +1         |       |

2 Select the *Pattern* radio button and then click the *Edit* button. The pattern editor will be opened.

**3** Assemble the pattern. For this purpose, click in the *Value* column pertaining to the required signals. If you keep the mouse button pressed, a box with suitable values appears (except for bus signals like *ADxx* or *CBEx\_x*, which require hex value inputs).

The signals of the pattern are automatically combined with a logical AND. For example, setting the *IRDY* and *TRDY* signals to "1" and entering *FBFFxxxx* as the value for the *AD32* address, will result in the boolean expression:

IRDY=1 && TRDY=1 && AD32=FBFFxxxx

4 After you have included all required conditions for your signals, click *OK*.

The pattern editor will be closed, and the pattern term will appear next to the *Pattern* radio button.

- 5 Check the correctness of the pattern term.

- **6** If you wish to delay the start of the master transactions an additional number of clock cycles, click the *Clockdelay* radio button and enter the number of clocks in 32-bit range (up to 4096 M).

- 7 Click *OK* to finish your conditional start setup.

## Starting the Master

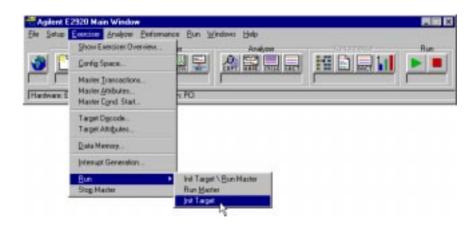

After you finished programming the master transactions along with master attributes and a start condition, if required, you can start your test. The different ways to run the master are:

- To run the master alone, select *Run > Run Master* from the *Exerciser* menu.

- To start several devices simultaneously, select *Start* from the *Run* menu, or.

click the Run button 上 in the main window.

For the latter cases, the settings in the Run Options window define which devices are started.

Master Run Status When the master is started, the entered transaction and attribute scripts are compiled. Internally, the master uses these settings to implement a state machine, which then performs all actions.

As a result, it requests bus access from the bus arbiter. When the bus is granted to the master, it drives the transactions on the bus as specified.

During the master run, the current status of the master is displayed in the status bar. Error status messages, such as *CE* for "Compare Error", will help you to identify and solve possible problems in your system under test.

Exerciser Status Bar

The following list explains every status that can be displayed in the Exerciser status bar:

- *Compiling.* The master is compiling the entries in the transaction editor and the attribute editor. No testcard programming is done yet.

- *Reinitializing*. The master and target state machines are programmed on the testcard.

- *Starting*. The master is going to be started.

- *Failed*. The start of the master or the initialization of the target has failed.

- Running. The master is running.

- *Stopped*. The master has stopped.

- CE. A data compare error occurred.

## **Stopping the Master**

If the master is not set up in repetitive mode, it will stop automatically after it has successfully performed the specified transactions.

However, you can also stop the master by hand. The different ways to manually terminate the master run are:

- clicking the Stop button 📕 in the main window,

- clicking the Stop button in the Run Options window,

- selecting *Stop Master* from the *Exerciser* menu,

- selecting *Stop* from the *Run* menu.

Manual Stop Required There can be situations in which the master does not finish the transactions, and you are then required to stop the master manually.

- The conditional start pattern does not occur on the bus and, thus, the master does not transfer any data.

- The master runs in repetitive mode.

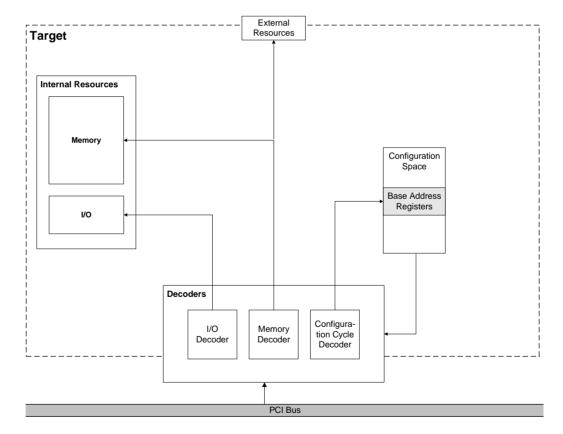

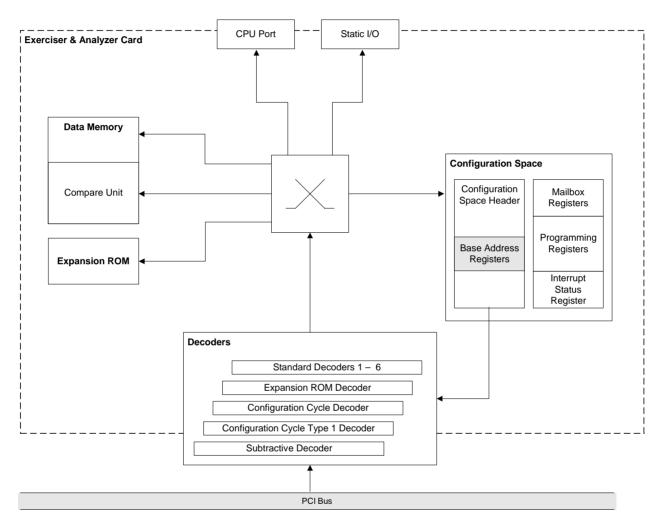

- The specified target only returns a retry on every initiated transaction.